# **Selection Guide**

### Input signals of the interface electronics

Interface electronics from HEIDENHAIN can be connected to encoders with sinusoidal signals of 1 V<sub>PP</sub> (voltage signals) or 11 µA<sub>PP</sub> (current signals). Encoders with the serial interfaces EnDat or SSI can also be connected to various interface electronics.

I<sub>1</sub>, A

I<sub>2</sub>, B

I<sub>0</sub>, R

U<sub>a0</sub>

0 -

#### Output signals of the interface electronics

Interface electronics with the following interfaces to the subsequent electronics are available:

- TTL square-wave pulse trains

- EnDat 2.2

- FANUC serial interfaceMitsubishi High Speed Serial Interface

- PCI bus

- Ethernet

- Profibus

## Interpolation of the sinusoidal input signals

In addition to being converted, the sinusoidal encoder signals are also interpolated in the interface electronics. This results in finer measuring steps, leading to an increased positioning accuracy and higher control quality.

## Formation of a position value

Some interface electronics have an integrated counting function. Starting from the last reference point set, an absolute position value is formed when the reference mark is traversed, and is output to the subsequent electronics.

### Measured value memory

Interface electronics with integrated measured value memory can buffer-save measured values: IK 220: Total of 8192 measured values *EIB 741:* Per input 250000 measured values

# Example of 5-fold interpolation Outputs Encoder signals Number Interface 360° elec. signal period 90° – Phase shift Reference-mark signal 2 Adjustable EnDat 2.2 1 Output signals after 5-fold interpolation FANUC serial interface 1 Mitsubishi High Speed Serial Interface Measuring step PCI bus 1 Reference pulse Ethernet 1 PROFIBUS DP 1

| Inputs                                                                                                        |        | Design – protection class       | Interpolation <sup>1)</sup> or subdivision | Model    |

|---------------------------------------------------------------------------------------------------------------|--------|---------------------------------|--------------------------------------------|----------|

| Interface                                                                                                     | Number |                                 |                                            |          |

| ∼ 1 Vpp                                                                                                       | 1      | Box design – IP 65              | 5/10-fold                                  | IBV 101  |

|                                                                                                               |        |                                 | 20/25/50/100-fold                          | IBV 102  |

|                                                                                                               |        |                                 | Without interpolation                      | IBV 600  |

|                                                                                                               |        |                                 | 25/50/100/200/400-fold                     | IBV 660  |

|                                                                                                               |        | Plug design – IP 40             | 5/10/20/25/50/100-fold                     | APE 371  |

|                                                                                                               |        | Version for integration – IP 00 | 5/10-fold                                  | IDP 181  |

|                                                                                                               |        |                                 | 20/25/50/100-fold                          | IDP 182  |

| ∕~ 11 μΑ <sub>ΡΡ</sub>                                                                                        | 1      | Box design – IP 65              | 5/10-fold                                  | EXE 101  |

|                                                                                                               |        |                                 | 20/25/50/100-fold                          | EXE 102  |

|                                                                                                               |        |                                 | Without/5-fold                             | EXE 602  |

|                                                                                                               |        |                                 | 25/50/100/200/400-fold                     | EXE 660  |

|                                                                                                               |        | Version for integration – IP 00 | 5-fold                                     | IDP 101  |

| ~ 1 Vpp                                                                                                       | 1      | Box design – IP 65              | 2-fold                                     | IBV 6072 |

|                                                                                                               |        |                                 | 5/10-fold                                  | IBV 6172 |

| ~ 1 V <sub>PP</sub>                                                                                           | 1      | Box design – IP 65              | ≤ 16384-fold subdivision                   | EIB 192  |

|                                                                                                               |        | Plug design – IP 40             | ≤ 16384-fold subdivision                   | EIB 392  |

| ∼ 1 Vpp                                                                                                       | 1      | Box design – IP 65              | $\leq$ 16384-fold subdivision              | EIB 192  |

|                                                                                                               |        | Plug design – IP 40             | ≤ 16384-fold subdivision                   | EIB 392  |

| ~ 1 V <sub>PP</sub>                                                                                           | 1      | Box design – IP 65              | ≤ 16384-fold subdivision                   | EIB 1921 |

|                                                                                                               |        | Plug design – IP 40             | ≤ 16384-fold subdivision                   | EIB 392  |

| √ 1 V <sub>PP</sub> √ 11 µA <sub>PP</sub> EnDat 2.1 / 01 SSI Adjustable                                       | 2      | Version for integration – IP 00 | ≤ 4096-fold subdivision                    | IK 220   |

| C 1 V <sub>PP</sub><br>EnDat 2.1<br>EnDat 2.2<br>C 11 μA <sub>PP</sub> upon request<br>Adjustable by software | 4      | Benchtop design – IP 40         | ≤ 4096-fold subdivision                    | EIB 741  |

| EnDat                                                                                                         | 1      | Top-hat rail design             | -                                          | PROFIBI  |

<sup>1)</sup> Switchable

# Interfaces Incremental Signals

The IBV, EXE, APE and IDP interpolation and digitalizing electronics from HEIDENHAIN convert the sinusoidal output signals from HEIDENHAIN encoders, with or without interpolation, into CLITTL square-wave signals.

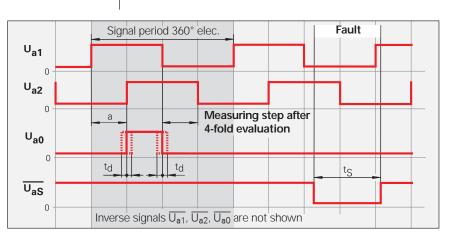

The **incremental signals** are transmitted as the square-wave pulse trains  $U_{a1}$  and  $U_{a2}$ , phase-shifted by 90° elec. The **reference mark signal** consists of one or more reference pulses  $U_{a0}$ , which are gated with the incremental signals. In addition, the integrated electronics produce their **inverted signals**  $U_{a1}$ ,  $U_{a2}$  and  $U_{a0}$  for noise-proof transmission.

The illustrated sequence of output signals—with  $U_{a2}$  lagging  $U_{a1}$ —applies to the direction of motion shown in the dimension drawing.

The **fault-detection signal**  $\overline{U_{aS}}$  indicates fault conditions such as breakage of the power line or failure of the light source. It can be used for such purposes as machine shut-off during automated production.

The distance between two successive edges of the incremental signals  $U_{a1}$  and  $U_{a2}$  through 1-fold, 2-fold or 4-fold evaluation is one **measuring step.**

The subsequent electronics must be designed to detect each edge of the square-wave pulse. The minimum edge separation a listed in the Specifications applies to the illustrated input circuitry with a cable length of 1 m, and refers to a measurement at the output of the differential line receiver. Propagation-time differences in cables additionally reduce the edge separation by 0.2 ns per meter of cable length. To prevent counting errors, design the subsequent electronics to process as little as 90% of the resulting edge separation. The max. permissible shaft speed or traversing velocity must never be exceeded.

| Interface                                             | Square-wave signals                                                                                                                                                                                                                                                            |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Incremental signals                                   | 2TTL square-wave signals $U_{a1}$ , $U_{a2}$ and their inverted signals $U_{a1}$ , $U_{a2}$                                                                                                                                                                                    |  |  |  |

| Reference-mark<br>signal<br>Pulse width<br>Delay time | 1 or more TTL square-wave pulses $U_{a0}$ and their inverted pulses $U_{a0}$<br>90° elec. (can be switched to 270° elec.)<br>$ t_d  \leq 50$ ns                                                                                                                                |  |  |  |

| Fault-detection<br>signal                             | <b>1TTL square-wave pulse <math>\overline{U_{aS}}</math></b><br>Improper function: LOW (switchable to three-state: $U_{a1}/U_{a2}$ high impedance)<br>Proper function: HIGH                                                                                                    |  |  |  |

| Pulse width                                           | $t_S \ge 20 \text{ ms}$<br>EXE 602E: $t_S \ge 250  \mu \text{s}$ can be switched to 40 ms                                                                                                                                                                                      |  |  |  |

| Signal levels                                         | Differential line driver as per EIA standard RS-422<br>$U_H \ge 2.5 \text{ V}$ at $-I_H = 20 \text{ mA}$<br>$U_L \le 0.5 \text{ V}$ at $-I_L = 20 \text{ mA}$                                                                                                                  |  |  |  |

| Permissible load                                      | $ \begin{array}{ll} Z_0 \geq 100 \ \Omega & \mbox{Between associated outputs} \\  I_L  \leq 20 \ \mbox{mA} & \mbox{Max. load per output} \\ C_{load} \leq 1000 \ \mbox{pF} & \mbox{With respect to 0 V} \\ \mbox{Outputs protected against short circuit to 0 V} \end{array} $ |  |  |  |

| <b>Switching times</b> (10 % to 90 %)                 | $t_+ / t \le 30$ ns (typically 10 ns) with 1 m cable and recommended input circuitry                                                                                                                                                                                           |  |  |  |

| Connecting cable<br>Cable length<br>Propagation time  | Shielded HEIDENHAIN cable<br>PUR [4(2 × 0.14 mm <sup>2</sup> ) + (4 × 0.5 mm <sup>2</sup> )]<br>Max. 100 m ( $\overline{U_{aS}}$ max. 50 m) at distributed capacitance 90 pF/m<br>6 ns/m                                                                                       |  |  |  |